~ミニマムな要素でチップレットを集積し、「ムーアの法則」の限界を打ち破る~

Chiplet, Semiconductor, Inegrated Circuit

サマリー

- 広帯域チップ間接続性能と集積規模拡大に優れたチップレット集積技術を開発。この技術は、微細な“MicroPillar”を用いたシリコン・ブリッジ接続構造と“All Chip-last”と呼ぶ製造プロセスにより実現。

- このチップレット集積技術は汎用性が高く、鈍化が見込まれる微細化に代わって今後の半導体集積回路システム技術の進化を加速すると期待される

- 栗田特任教授は、この技術を含むチップレット集積技術の産業化のためにコンソーシアムを設立、多数の参加企業と共同研究をしている。

今後のIC性能向上の切り札「チップレット集積技術」

デジタル社会を支える半導体集積回路(IC)。20世紀中頃に発明されて以来、微細加工技術の進歩により集積度は上がり続け、「1個のチップに搭載されるトランジスタの数は約2年で2倍になる」という「ムーアの法則」がずっと成り立ってきました。集積度と共に性能が向上してきたことは言うまでもありません。しかし、現在の半導体回路のサイズは数nmとほぼ原子のサイズに達しています。これ以上の微細化は難しいため、ムーアの法則も終焉が近いというのが業界の認識です。

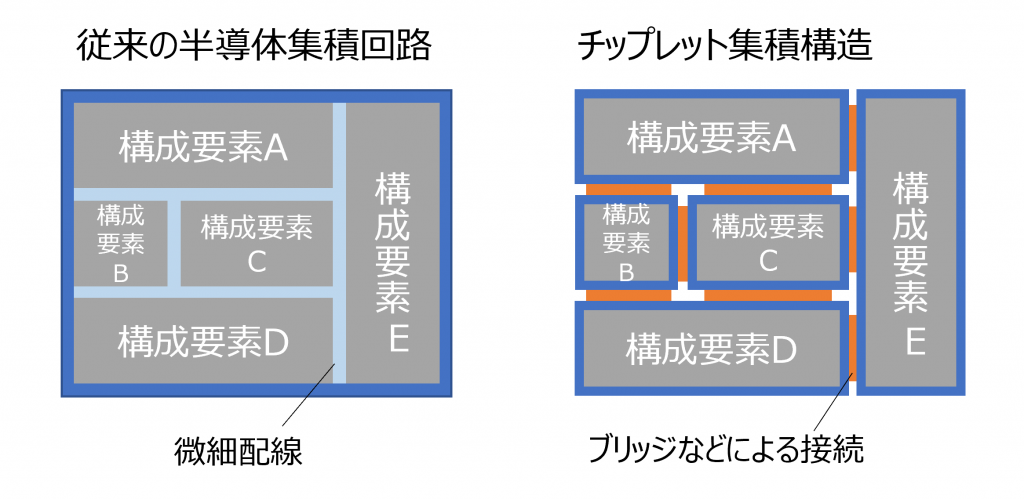

「そこで注目されているのが、微細化とは異なる発想でICの性能向上を目指すチップレット集積技術です(図1)」と栗田特任教授はいいます。チップレット集積とは、1個のチップにすべての構成要素を搭載するのではなく、構成要素ごとに小さいチップ(チップレット)をつくり、それらを密に接続して集合体とすることです。そのメリットを栗田特任教授は、「チップレットごとに異なる構造や製造法を採用できるので、性能の向上を図りやすいのです。チップレットの組み合わせ方により、さまざまなニーズに柔軟に応えることもできます」と説明します。

従来は1個のチップの上にさまざまな構成要素をつくりこみ、構成要素の間の配線もチップ上につくりこんでいた。チップレット集積構造では、構成要素をブロックのように独立したチップレットとしてつくり、組み合わせる。構成要素間は後述のブリッジなど別の要素で接続する。

いいことずくめのシンプルな接続技術

すでに欧米の半導体大手がチップレット集積によるプロセッサを製品化するなど、実用化に向けての動きは急ですが、課題もあります。なかでも大きな課題は、チップレット同士をどう接続するかです。チップレット間を広帯域接続するためにさまざまな方法が模索されている中、栗田特任教授は、接続に必要な要素が圧倒的に少ない、シンプルな接続技術を開発しました。接続構造がシンプルなため、製造工程も少なくてすみ、性能の高い製品を低コストで製造することが可能になります。

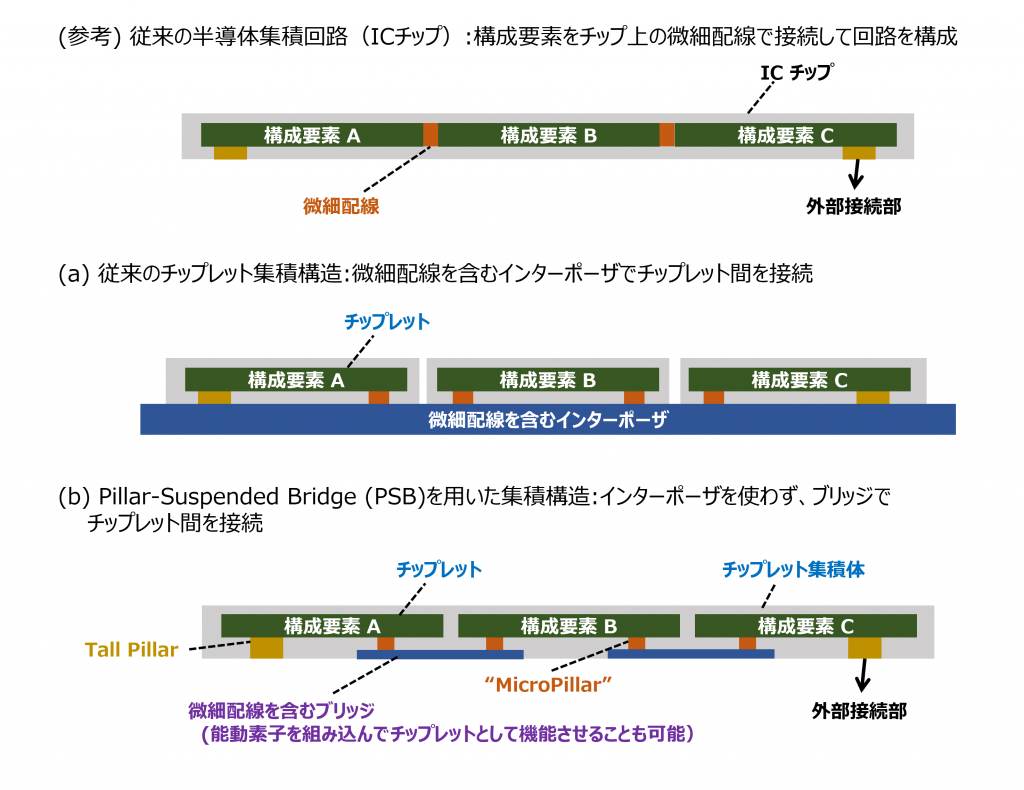

栗田特任教授が開発した接続技術は、「インターポーザ・レス」であることが特徴です(図2)。「従来技術では、高密度配線を含むインターポーザの上にチップレットを配置して接続します。このため、製造には複雑な工程が必要です。また、チップレット間を、『シリコン・ブリッジ』とよばれる小さな配線チップでつなぐ既存技術もありますが、その場合もインターポーザを使います」。

栗田特任教授の技術もシリコン・ブリッジを採用していますが、“MicroPillar”とよぶ金属柱でシリコン・ブリッジをぶら下げる構造をとっているため、インターポーザは不要です。栗田特任教授は、この構造と製造プロセスを“Pillar-Suspended Bridge (PSB)” 技術と名付けました。「PSB構造では接続のための要素を最小限に抑えているため、製造ステップは少なくてすみます。さらに、インターポーザの大きさの制約を受けないので、チップレットの数を増やせば大規模な集積システムをつくれるスケーラビリティも大きな特徴です」と栗田特任教授は説明します。

従来構造(a)では、インターポーザを使用するため、製造工程が複雑になり、大型化もしにくい。一方、PSB構造では、MicroPillarでブリッジをぶら下げており、インターポーザを使用しない。製造工程は簡素化され、大型化も容易である。

PSB接続技術をテコに日本の半導体産業を活性化したい

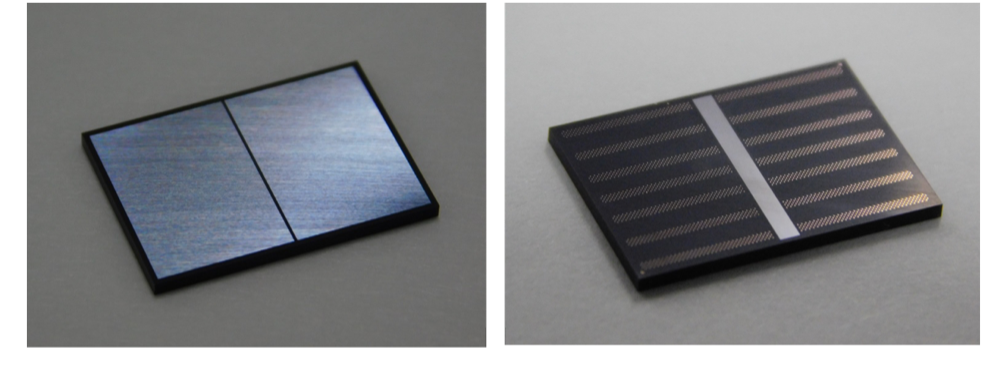

栗田特任教授はPSB技術のコンセプト実証のため、サンプルを作製しました(図3)。2個のチップレットを接続した集積体を、パネル上に多数つくり、切り出したものです。「巨大なパネルでの製造でしたので、反りや変形をコントロールし、高密度な接続を実現するための構造/プロセス設計や材料選択が重要でした」と苦労はありましたが、“All Chip-last”という製造プロセスを開発することにより、狙い通りの集積構造の作製に成功しました。

左は2個のチップレットが露出している面。右はブリッジ(中央)と電極端子群が露出している面。サイズは約10mm x 15mm×0.5mm。

このPSB構造は、大規模化が容易なだけでなく、Fan-Out 機能をもつ配線層を重ねることで高度な機能をもたせることも可能です。将来的には、「この技術で作製した集積システムのハイエンドのアプリケーションとしてAI/HPCが考えられます。未確認ですが信頼性も期待できるので、自動運転やコンシューマ向けなど、広い用途に使えると思います」と栗田特任教授は期待しています。

この画期的な技術を中心とした日本のチップレット集積技術を向上させ、産業化することを目的として、栗田特任教授は2022年10月に「チップレット集積プラットフォーム・コンソーシアム」を立ち上げました。すでに数十の企業と、東京工業大学、大阪大学、東北大学が参加しています。

このコンソーシアムでは、チップレット集積プラットフォームを「装置・材料〜集積ファウンドリ〜設計/アプリ」というバリュー・チェーンでとらえ、各段階で大学の研究者がリーダーシップをとりつつ複数の企業が共同研究を行うことを計画しています。「具体的には、HPCなどのアプリケーションのニーズから、集積回路設計とリンクしたシステム最適化、システム全体のハードウェア(パワーデリバリ/広帯域入出力など)の開発をしたいと思っています」

チップレット集積技術の国際競争は激しいので、その中で日本が生き残れるよう、コンソーシアムを強力な組織にしたいというのが栗田特任教授の願いです。「ぜひ、多くの企業の皆さんにコンソーシアムに参加していただきたいです。特に、我々は製造が中心ですので、顧客であるシステムやファブレス半導体企業と共同研究し、ニーズを教えていただくことが最も重要だと考えています。興味がおありの企業の方は、直接ご連絡ください(※)」

※ kurita.y.ac(at)m.titech.ac.jp (at)を@に置き換えて下さい

参考リンク

Flintbox

Chiplet Integration Architecture using Pillar-Suspende Bridge

https://oip-titech.flintbox.com/technologies/1ae36c5e-c72b-4bc3-a452-5226b1616ef9

東工大ニュース

最小要素のチップレット集積技術を開発

広帯域接続と集積規模のスケーラビリティを実現

https://www.titech.ac.jp/news/2022/064932